**Technical Report No. SNU-EE-TR-1997-5**

# VHDL Developer's Toolkit 2.6 User's Guide & Reference

Sanghun Park Kiyoung Choi

September 1997

School of Electrical Engineering Seoul National University

## Copyright ã 1997 by Sanghun Park and Kiyoung Choi

Haedong Digital Library Room 312, Building 301, Seoul National University Shinlim-dong, Kwanak-gu, Seoul 151-742, Korea Tel: (02)880-1787 Fax: (02)882-4656 http://haedong.snu.ac.kr

## **Abstract**

This report presents VDT (VHDL Developer's Toolkit) which has been developed to support fast and easy development and integration of VHDL application tools. VDT is a software package which is developed using object-oriented programming language. The toolkit provides a library of versatile routines and several utilities. As basic utilities, it provides a VHDL analyzer and a VHDL generator. The VHDL analyzer parses the given VHDL code and constructs the intermediate form. The VHDL generator regenerates the corresponding VHDL code from the given intermediate form. The toolkit also provides a procedural interface through which application tools can efficiently manipulate VHDL intermediate forms. Procedural interface is a library of versatile routines which are used to handle the intermediate form. The toolkit is based on a data model which has been designed to represent the basic structure of the VHDL intermediate form. The data model supports the full set of IEEE Std 1076-1987.

## **Table of Contents**

| 1 Introduction                      | £µ              |

|-------------------------------------|-----------------|

| 2 Structure of VDT                  | £¶              |

| 3 Data Model                        | £,              |

| 3.1 Abstract VDT data model         | £,              |

| 3.2 Data structure of VDT objects   | £ £ ±           |

| 3.3 Classification of basic objects | £ £ 2           |

| 3.4 Relationship checking           | ££ <sup>3</sup> |

| 3.5 Object-oriented Programming     | ££μ             |

| 4 Intermediate Form Representation  | ££¶             |

| 4.1 Architecture body               | ££¶             |

| 4.2 Process Statement               | ££¶             |

| 4.3 Signal Assignment Statement     | ££·             |

| 5 Procedural Interface              | ££ <sup>1</sup> |

| 5.1 Library Object Management       | ££°             |

| 5.1.1 Open/Close Routine            | ££±             |

| 5.1.2 Add/Sub/Gen Routine           | £ £ 2           |

| 5.1.3 Get Routine                   | ff <sup>3</sup> |

| 5.1.4 Search Routine                | ££´             |

| 5.1.5 Dump Routine               | £ξμ              |

|----------------------------------|------------------|

| 5.2 Design Unit Management       | ££·              |

| 5.2.1 Load/Save Routine          | ££,              |

| 5.2.2 Create Routine             | ££°              |

| 5.2.3 Get Routine                | ££±              |

| 5.2.4 Dump Routine               | ££±              |

| 5.2.5 Generate Routine           | ££2              |

| 5.2.6 Check Routine              | f f 3            |

| 5.3 Library Unit Management      | ££´              |

| 5.3.1 Set/Get Routine            | ££´              |

| 5.3.2 Add/Sub/Gen Routine        | ££¶              |

| 5.3.3 Get routine                | ££.              |

| 5.3.4 Search Routine             | ££·              |

| 5.3.5 Dump Routine               | ££,              |

| 5.3.6 Generate Routine           | £ £ <sup>1</sup> |

| 5.3.7 Check Routine              | ££°              |

| 5.3.8 Characterize Routine       | ££°              |

| 6 Characterize Routines          | ££²              |

| 6.1 Class identifying routines   | ££²              |

| 6.2 Group identifying routines   | ££´              |

| 6.3 Property getting routines    | ££ <sup>1</sup>  |

| 7 VDT Utilities                  | £ f <sup>2</sup> |

| 7.1 VHDL Analyzer                | £ f ²            |

| 7.2 VHDL Code Generator          | £ f ²            |

| 7.3 VHDL Static Semantic Checker | £ f <sup>3</sup> |

| 7.4 Design Library Browser       | £ f <sup>3</sup> |

| 7.5 Intermediate Form Dumper     | £ f <sup>3</sup> |

| 7.6 IF to BLIF Translator                          | £p´              |

|----------------------------------------------------|------------------|

| 7.7 BDNET to VHDL Translator                       | £µ´              |

| 8 Appendix A. VDT Object Definition                | £µ·              |

| 9 Appendix B. Naming Rule                          | £££ <sup>3</sup> |

| 10 Appendix C. FSM Synthesis from VHDL Description | £££µ             |

| 11 Appendix D. VDT Installation                    | £££,             |

## **1** Introduction

Since 1987, when VHDL (VHSIC Hardware Description Language) became the formal international standard[1], the language has been gaining its popularity due to the widespread top-down design methodology and the increasing need for ASICs (Application Specific Integrated Circuits) [2,3,4]. Although much effort has been put for the development of VHDL libraries and tools [5,6,7], the increasing design size and complexity are still pushing the tool developers for more and better libraries and tools. However, it is not an easy task to develop tools that support the broad range of VHDL's descriptive capability while maintaining good performance. The development takes a long time and much effort because every tool needs to be able to analyze VHDL descriptions, deal with complex intermediate data, and/or give much consideration to obtaining efficient data access.

The development of VDT (VHDL Developer's Toolkit) aims at providing a set of tools and an integrated environment to tool-developers so that they can speed up the development and integration of VHDL-related tools. The basic concept of VDT is similar to that of other existing systems such as the IBM VHDL Design System [8] and CLSI's VTIP(VHDL Tool Integration Platform) [9]. However, the internal structure of the existing systems are unclear and complex, and therefore, the systems are difficult to use. VDT has been built on a data model which is relatively simple but still maintains the full VHDL descriptive power. VDT also provides a clear procedural interface between applications and the intermediate form.

This report is structured as follows. The next section presents the structural overview of VDT. Section 3 explains the design of the data model that forms the basis for VDT. Section 4 explains the implementation aspect on data structure. Section 5 explains the intermediate form representation for various VHDL constructs. Section 6 explains the procedural interface in detail. Section 7 presents the method by which VDT utilities are developed and integrated into VDT.

## 2 Structure of VDT

VDT is a software package which is developed using the C++ programming language. This package includes a library of versatile routines and several basic tools which enable easy and quick development of VHDL application tools. The core module of the toolkit is PI (Procedural Interface) which is a library through which application tools can efficiently manipulate VHDL intermediate forms. As basic tools provided by the toolkit, there is the VHDL analyzer, VHDL generator, library browser, and so on. The toolkit is based on a data model which has been designed to represent the basic structure of the VHDL intermediate form. The data model supports the full set of IEEE Std 1076-1987.

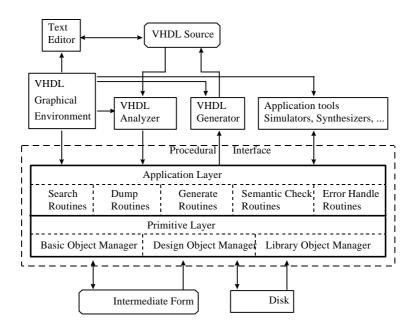

Figure 1. Structure of VHDL Developer's Toolkit

Figure 1 shows how the basic tools and utilities are configured together with other application tools, such as simulators and synthesizers. PI consists of two stacked layers. The primitive layer contains routines for primitive operations on library objects, design objects, and basic objects. These three kinds of objects form a hierarchy in the intermediate form. The application tools call on these routines to access the intermediate form. The VHDL analyzer, for example, analyzes a VHDL source and construct the intermediate form by calling on various routines in PI. Then it calls for the semantic check routines to see if the VHDL source has correct semantics. If it passes the semantic checking, the intermediate form is stored onto the disk in the form of well-arranged binary data. Because the basic routines, such as building and storing an intermediate form, are provided by PI, the analyzer could be developed quickly and easily. With this toolkit, developing application tools such as simulators are easy because all the routines for manipulating the intermediate form and even the analyzer are already there ready to be used.

Because the intermediate form preserves all the semantics implied by the original VHDL code, any application tool can use the same intermediate form as its inputs. VHDL code can be regenerated from a given intermediate form by the VHDL generator. The generated VHDL code may look different from the original code, but must have the same semantics.

## **3** Data Model

Because of the wide range of descriptive capability of VHDL, high complexity of the intermediate form is unavoidable. Accordingly, the manipulation of the VHDL intermediate form is a very complicated and errorprone process. However, we can alleviate the problem by designing and utilizing a data model which is a notation for representing the structure of intermediate forms. The data model can be used by both the PI developers and the application tool developers. The PI developers write procedures such that the procedures can manipulate the intermediate forms according to the data model. The application tool developers use the data model to understand how the intermediate form is structured and how it is accessed through PI's procedures.

In designing the data model, the following aspects are considered:

- The data model must be designed such that the full VHDL descriptive capability is kept intact in the intermediate form representation. No loss of information is allowed during the analysis process.

- The data model partially supports the VHDL semantics. Full support would cause too much overhead. Therefore, it is possible to build an intermediate form that is semantically incorrect but conforms to the data model. Detecting such an error is the job of the Semantic Checker module of PI.

- Efficiency (memory space and speed) is one of the most important factors that must be considered in designing the data model. The efficiency in manipulating intermediate forms affects the performance of every application tool and must be considered in the data model design phase.

- Application tool developers are expected to use the data model as a 'map' for accessing the intermediate form. Therefore, the data model must be as simple as possible so that the user can understand the structure of the intermediate form without too much difficulty.

## 3.1 Abstract VDT data model

The top-most VHDL construct is a design library. A design library is a host dependent storage facility for the intermediate forms of the analyzed design units. The second highest construct is a design unit. A design unit can be analyzed independently, and an intermediate form is constructed. The intermediate form can be stored in a design library. Usually, a design library is implemented as a directory of file system, whereas a design unit is implemented as a file stored in the directory. A design unit is composed of a library unit and a context clause. There are five kinds of VHDL constructs called library units: entity declaration, package declaration, configuration declaration, architecture body, and package body. The context clause proves the context in which a library unit is analyzed. As the lowest VHDL constructs, there are signal declaration, process statement, case statement, configuration specification, and so on. A design unit is composed of these constructs.

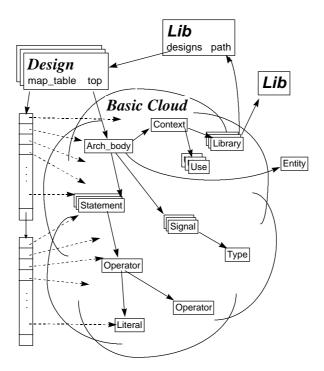

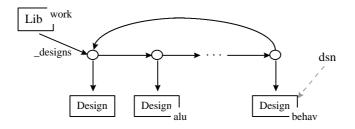

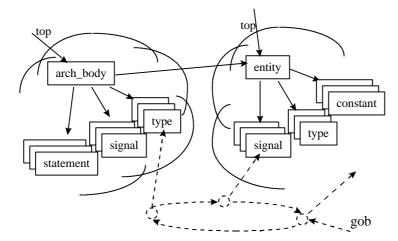

Figure 2. Abstract VDT data model.

Figure 2 shows an abstraction of VDT data model. VDT data model defines the general structure of intermediate forms. An intermediate form is composed of many kinds of objects which we call VDT objects. All VHDL constructs are described by VDT objects in an intermediate form representation. For each VDT object, there is a corresponding VHDL construct. An intermediate form can be modeled as a directed graph, where vertices represent VDT objects and edges represent the relationships.

VDT objects can be classified into three kinds; lib object, design object, and basic object. Lib object represents a design library, design object represents a design unit, and basic objects represents the rest of VHDL constructs. For instance, in an intermediate form representation, an architecture body is represented by an Arch\_body object and a type declaration is described by a Type object. The Arch\_body objects and Type objects are basic objects. A basic cloud is composed of only basic objects and relationships among these objects. Actually, the behavior of a circuit is described by a basic cloud. On the other hand, lib objects and design objects contain only the information on the environment. In the programmer's view, the design object can be regarded as a container of basic objects. Similarly, a lib object can be regarded as a container of design object.

## 3.2 Relationships among basic objects

A relationship associates an object with other objects. For example, an object corresponding to a signal of bit type has a relationship to the bit type object. A relationship from an object can be one-to-one or one-to-many depending on how many objects are associated with the object.

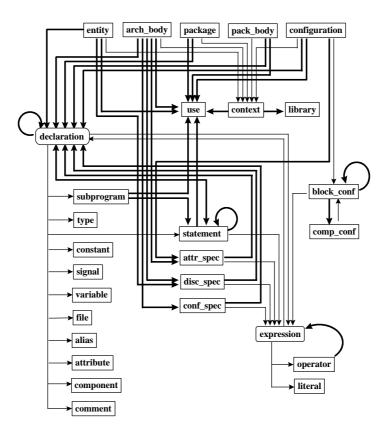

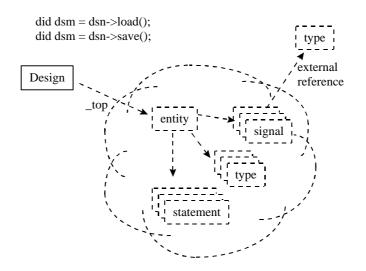

Figure 3. Relationships among VDT basic objects.

Figure 3 shows the detailed data model diagram of VDT basic objects and relationships among these objects. In these figures, a rectangular box represents an object type whereas an arc-box represents a class. Thin arrows represent one-to-one relationships whereas thick arrows represent one-to-many relationships.

Relationships across design units, those which are associations among Basic objects that are in different Basic clouds, are called external references. In Figure 2, the relationship from the Arch\_body object to the Entity object is an external reference. When design object is stored onto the disk as a file, all basic objects contained within the corresponding basic cloud are also stored. However, the external references are broken during the storing of a design unit. The external references are restored when the design object and the basic cloud are loaded. For this purpose, the information on the external references are kept in the basic cloud.

## **3.2** Data structure of VDT objects

Given the data model, memory usage and performance are the key criteria in designing the data structure. Each object type in the data model is implemented by the class construct of the C++ programming language. Each attribute and relationship is implemented by a private member of the class. The access routines of these fields are implemented by member functions.

The data structure of VDT objects has many storage fields to capture a given VHDL description. These storage fields can be classified into two categories: attribute fields and relationship fields. The relationship fields store the pointer of a related object, which describes the relationship with the object. For instance, Signal object has a relationship field "type" to point a Type object that corresponds to a type of the signal. On the other hand, the attribute fields store the properties of object itself and corresponding VHDL construct, such as object sequence number, code line number, identifier, and so on.

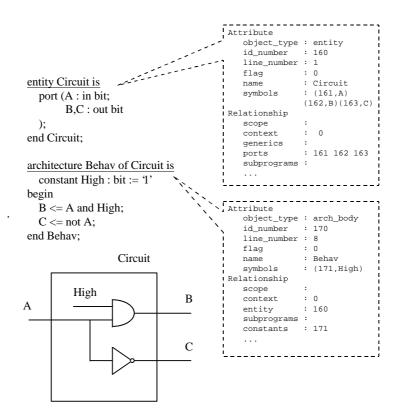

Figure 4. Data structure of VDT object.

Figure 4 shows the contents of two objects corresponding to entity declaration and architecture body. The architecture body has an identifier "Behav". This identifier is captured by the attribute field "name" of Arch\_body object. The architecture body is associated with an entity declaration called "Circuit". This relationship is captured by the relationship field "entity".

Actually, the attribute values of VDT objects must be of type, such as string, integer, and user defined enumeration. All kinds of basic objects have some attribute fields in common, such as "object\_type", "id\_number", "line\_number", and so on. The field "object\_type" represents the kind of basic object. The field "id\_number" represents the sequence number of basic object and identifies a unique basic object within a design unit. The field "line\_number" represents the line number on which the corresponding VHDL construct appears in VHDL file.

There are two kinds of relationship, one-to-one relationship and one-to-many relationship. The one-to-one relationship field can point only at one object. The one-to-many relationship field can point at many objects. The naming convention distinguishes the two names of the one-to-one relationship field and one-to-many relationship field. If the name of a relationship field is an identifier with the ending 's', then the field is for one-to-many relationship. Otherwise, the field is for one-to-one relationship. The values of relationship fields must be the pointer of VDT object. When the contents of VDT objects are stored on disk or are printed on screen, the pointer value is replaced by the sequence number "id\_number" of the pointed object.

VDT naming rule makes the convention on abbreviated names of VDT objects and the storage fields of these objects. For instances, Arch\_body represents an object corresponding to architecture body, the relationship field "constants" of Arch\_body object represents the list of constants declared within the architecture body.

## 3.3 Classification of basic objects

For each basic objects, there is a unique data structure. Basic objects can be distinguished by many kinds, as many as the kinds of VHDL constructs. For instances, a Signal object describes a signal declaration, a Conf\_spec object describes a configuration specification in an intermediate form representation.

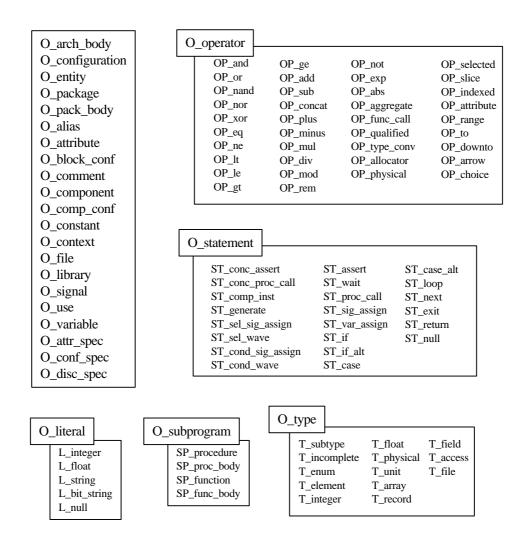

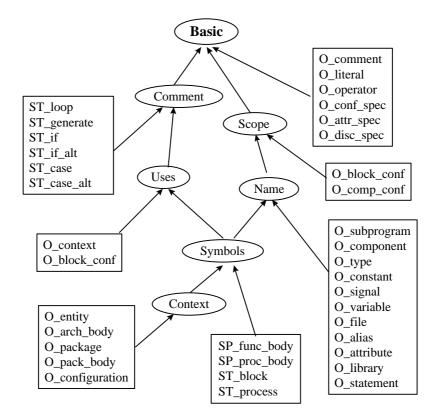

Figure 5. Basic object kinds.

Figure 5 shows the kinds of basic objects. Basic objects are identified by attribute field "object\_type" whose type is of predefined enumeration type. The enumeration type named object\_type has many elements shown in the above figure. O\_arch\_body is the object\_type value of Arch\_body object which is a kind of Basic object corresponding to architecture body. Simply, Arch\_body object is called O\_arch\_body without confusion.

Several basic objects are divided more precisely. The related objects are O\_literal, O\_operator, O\_statement, O\_subprogram, and O\_type. O\_literal is classified in more detail into five kinds: L\_integer, L\_float, L\_string, L\_bit\_string, and L\_null. L\_string is a kind of Literal objects, and corresponds to string\_literal. Simply, a Literal object having "L\_string" kind is called L\_string without confusion.

## 3.4 Relationship checking

An individual intermediate form is constructed by analysis of a VHDL description that corresponds to a design unit. VHDL description is captured by VDT objects and the relationships among these objects in an intermediate form representation.

An intermediate form is composed of VDT objects and the relationships among these objects. The intermediate form representation can be regarded as a directed graph, where vertexes represent VDT objects, and edges represent the relationships among these objects.

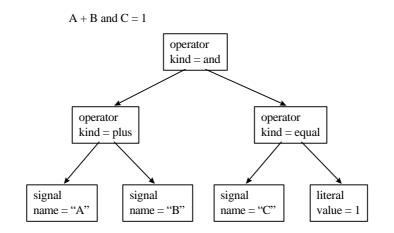

Figure 6. Representation of intermediate form

Figure 6 shows an example of intermediate form representation which corresponds to a VHDL expression. The intermediate form is composed of seven VDT objects and six relationships. The "and" operator is represented by OP\_and, and "+", "=" operators are by OP\_plus, OP\_equal, respectively. The operands "A", "B", "C" are represented by O\_signal, and the operand "1" is represented by L\_integer.

The binary operators have two relationships that indicate the two operands respectively. In the above figure, the two relationships are represented by two directed arrows from an operator to the operands.

An intermediate form constructed by analysis of a design unit contains all syntax and semantics of a given VHDL description. If a given VHDL code has illegal syntax and semantics, the constructed intermediate form may contain these illegal syntax and semantics. For instance, a signal declaration creates a signal of the specified type. The corresponding O\_signal has a relationship with O\_type corresponding to the specified type. The object allowed to be linked with O\_signal for this relationship are only O\_type or Basic object regarded to a type.

The relationship checking does check if the relationship being made is legal by definition of VDT data model. Namely, the relationships defined by VDT data model restrict illegal intermediate form containing illegal syntax and semantics. But all illegal syntax and semantics cannot be restricted by these relationship definitions. So, an intermediate form may contain some illegal syntax and semantics. These remained illegalities can be removed by the analyzer and semantic checker.

#### 3.5 Object-oriented Programming

VDT is developed by using C++ programming language[10], which is an object-oriented programming language. Object-oriented technique has three powerful features: data abstraction, inheritance, and polymorphism. VDT data model and PI library are implemented by fully using these features.

Data abstraction is provided by a *class* construct in C++ language. Each VDT object is implemented to a unique *class*. A *class* consists of a data structure and member functions that handle the data structure. Only the member functions of a class can access the associated data structure. A class construct provides protection mechanism that protects the accessing of a corresponding data structure from outside of a class.

Inheritance is accomplished by class hierarchy in C++ language. All classes corresponding to Basic objects are derived from one base class. All derived classes are cast to this base class, and inherit the storage fields and member functions of the base class. This inheritance mechanism enables code sharing among different classes. The code sharing is accomplished by defining a class with common storage fields and access routines, and by inheriting this class.

Polymorphism is accomplished by virtual function in C++ language. Each Basic object is implemented to a unique class that may have some common members to other class by inheriting from the same classes. A given Basic object may not have some member functions. A calling of these member functions for this object will cause error.

## 4 Intermediate Form Representation

In the programmer's view, there are containment relation among VHDL constructs. Design library is a VHDL construct larger than design unit and contains many design units. Design unit is a construct larger than entity declaration and contains many of these constructs. Entity declaration is a construct larger than signal declaration, constant declaration, etc.

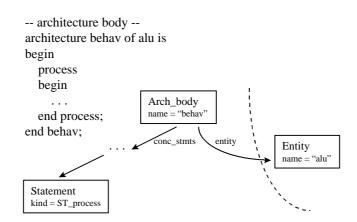

## 4.1 Architecture body

Figure 7 shows the intermediate form representation corresponding to an architecture body. A process statement appears in architecture body. The architecture body and process statement are represented by Arch\_body object named "behav" and Statement object, respectively. O\_arch\_body is Arch\_body object, and ST\_process is a Statement object attributed with ST\_process kind. O\_arch\_body has a connection with ST\_process, which represents the relation between architecture body and process statement.

Figure 7. Intermediate form representation for architecture body.

The data structure of Arch\_body object has a attribute field named "name" which is of a string type and is written as "behav" in this example. And, it has a relationship field named "entity" which is of a pointer type and is written as the address of Entity object. It also has a relationship field named "conc\_stmts" which is of a pointer array type. In this example, one ST\_process is pointed by the "conc\_stmts" field of Arch\_body object. In addition, the data structure of Arch\_body object has many fields.

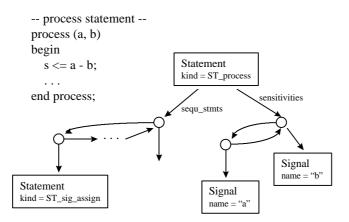

## 4.2 Process Statement

In process statement, sensitivity list can appear. Sensitivity list indicates the signals that activate the process statement during simulation. ST\_process has one-to-many relationship with these signals, and the objects related to "sensitivities" relationship of ST\_process can be O\_signal or objects that can be regarded to signal such as a

signal attribute and a slice name of a signal. If it tries to make a relation with no signal object, error message will be reported by relationship checking routine of PI.

Figure 8. Intermediate form representation of process statement.

Figure 8 shows the intermediate form representation corresponding to a process statement which contains many sensitivities and many sequential statements. The process statement is represented by ST\_process. ST\_process has sequ\_stmts and sensitivities fields to describe the relations with sequential statements and sensitivities, respectively.

The containment relation is implemented to the directed pointer. The ST\_process has the storage field named "sequ\_stmts" and "sensitivities" of a pointer array type. The "sequ\_stmts" field points the objects corresponding to sequential statements contained in this process statement. Actually, the pointer array is a single-linked list which enables easy append, deletion, and sequential searching.

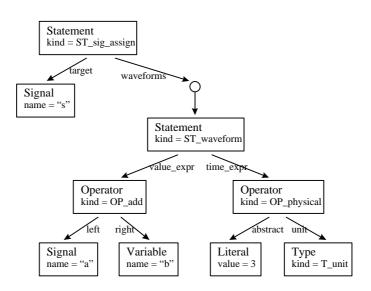

## 4.3 Signal Assignment Statement

Figure 9 shows the intermediate form representation corresponding to signal assignment statement. A signal assignment statement is described by a ST\_sig\_assign in intermediate form. ST\_sig\_assign has "target" and "waveforms" relationships. The "target" relationship is 1:1 relationship and relates to an object corresponding to target. The "waveforms" relationship is 1:m relationship and relates to objects corresponding to waveform element list.

-- signal assignment statement -- s <= a + b after 3 ms;

Figure 9. Intermediate form representation of signal assignment statement.

The syntax of waveform is "value\_expression AFTER time\_expression". ST\_waveform is the Basic object corresponding to the waveform. ST\_waveform has two relationships: "value\_expr" and "time\_expr" relationship. The "value\_expr" relationship describes the relation to the value expression and points an object corresponding to an expression. The "time\_expr" relationship describes its relation to the time expression, and points an object corresponding to an expression.

## **5 Procedural Interface**

The core module of this toolkit is PI, which is a library of versatile routines that handle the intermediate form. The intermediate form is protected to be accessed by a pointer. The user can handle the intermediate form only through the routines provided by PI. PI library can be divided to three modules according to the related VDT object, design library manager, design unit manager, and library unit manager. According to library hierarchy, PI can be divided into two layers: primitive layer and application layer. The routines within primitive layer access directly the data structure of VDT object. On the other hand, the routines within application layer can not access the internal data of VDT object, but do more complex processing by using the routines within primitive layer.

The data structures are defined for each VDT object. And the access routines of an object are defined mutually for each field. The routines included in PI range up to several hundreds. It is hard to remember all the names of routines. The name of an access routine is a combined one with the name of a related storage field. This naming convention of routines enables a fast and easy recognition of the function of a routine.

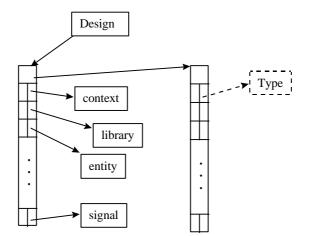

PI library can be divided to three modules according to the related VDT object: library object manager, design object manager, and basic object manager. The module of library object management handles lib object which corresponds to the largest VHDL construct called design library. Design library is the storing location of design units and actually associated with a directory of file system. This module defines the data structure of lib object, and contains a few routines handling this object. The module of design object management handles design object which corresponds to the second largest VHDL construct called design unit. Design unit is an atomic unit which can be analyzed independently to other units. An intermediate form constructed by analysis of a design unit is stored as a file in a given directory. This module defines the data structure of design object, and contains a few routines handling this object. The module of basic object management handles basic object. All VHDL constructs except design unit and design library are represented by basic object in an intermediate form. Basic object is classified into many kinds. This module defines the data structures of each Basic object, and contains numerous routines handling these objects. The size of this module is very much larger than other modules, and most PI libraries are occupied by this module.

All routines in PI library can be classified into two categories: access routine and processing routine. The access routines read and write directly the data structure of VDT object. On the other hand, the processing routines just process the information of VDT object by using the access routines. The access routines are located in the primitive layer of PI, and the processing routines are located in a higher layer called the application layer of PI. The access routines can be classified into three categories according to related storage field of the data structure: attribute getting routine, 1:1 relationship making routine, and 1:m relationship making routine. The attribute getting routine reads a given storage field which is regarded as an attribute field. The 1:1 relationship making routine gets the object linked to a related 1:1 relationship field, and links a given object to that field. The 1:m

relationship making routine gets the object list linked to a related 1:m relationship field, and links a given object to that field.

## 5.1 Library Object Management

This module has a few access routines and processing routines. As access routines, there are "open/close" routines, "add/sub/gen" routines, and "get" routine. As processing routines, there are "search" and "dump" routines.

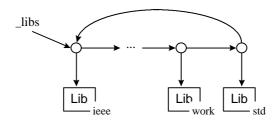

The creation of a new design library is accomplished by just assigning the logical name of design library to a directory path-name of UNIX file system. The configuration is written to a special file named "\$VDT/etc/.VDTRC". Figure 10 shows the contents of this configuration file. This file configures basically the design library named "STD" and "WORK", and includes other configuration files named "~/.vdtrc" and ".vdtrc".

-- contents of start-up file --Library STD \$VDT/etc/std Library WORK . Include ~/.vdtrc Include ./.vdtrc

static SLList<Lib\*> gLib::\_libs;

Figure 10. Create a design library.

All tools using VDT initially read the configuration file and automatically build the list of Lib objects. This list exists while a program is running and can be increased and decreased. If there is any error in a configuration file, a program cannot be run. The above is the syntax of design library configuration.

• Synopsis of new design library creation.

LIBRARY str1 str2 char\* str1; -- logical design library name.

char\* str2; -- path-name of a directory.

In default, there are three configuration files which have the precedence. If there are one more configuration for the same design library with different path-name, then the last configuration overrides.

## 5.1.1 Open/Close Routine

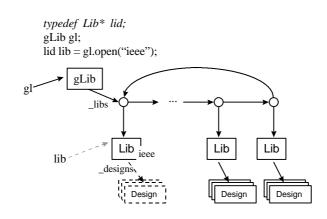

A Lib object represents a design library and captures the information of a directory corresponding to the design library such as path-name of the directory, the count of design units within the design library, and so on. Figure 11 shows the C++ code of open routine and the result of that running for "ieee" design library.

Figure 11. Open design library.

The type of "gLib" is predefined by PI library as a list of Lib objects. The type of "lid" is also predefined as a pointer of Lib object. The open routine is accomplished to a variable "gl" of "gLib" type with logical design library name "ieee". As a result, the variable "lib" gets the pointer of Lib object named "ieee" which is found in the list of Lib objects. During the processing of open routine, the files within a directory which are of VDT intermediate forms are collected and built to Design objects.

- Synopsis of open routine.

- #include "libraryMan.h"

- lid gl.open(str)

- gLib gl; -- variable of gLib type.

- char\* str; -- logical design library name.

#### Description

- a. Find a Lib object for a given logical library name in the list of Lib objects.

- b. Open a directory corresponding to the Lib object.

- c. Collect files which are the saved images of VDT intermediate form.

- d. Create a Design object for each file.

- e. Append each created Design object to Lib object.

- f. Close the directory.

- g. Return the pointer of the found Lib object. If not found, return Null pointer.

cf) If a Lib object is already opened, the repeated running of open routine for the same Lib object will not accomplished. It saves the computing time and guarantees only one existence of the same Lib object in the

system.

- Synopsis of close routine.

- #include "libraryMan.h"

- lid gl.close(str)

- gLib gl; -- variable of gLib type.

- char\* str; -- logical design library name.

## Description

- a. Find the Lib object for a given logical design library name.

- b. Save each Design object to a file in the form of well-arranged binary data.

- c. Locate the file in the directory corresponding to the Lib object.

- d. Return the pointer of Lib object. If error occurs, return Null pointer.

- cf) After the running of close routine, all data structures are resident in system until a program finishes.

## 5.1.2 Add/Sub/Gen Routine

A Lib object can contain one or more than one Design objects, and holds these objects as a list. This list represents the 1:m relationship between design library and design unit. A Design object can be added to, subtracted from, and referred to the list freely using PI routines.

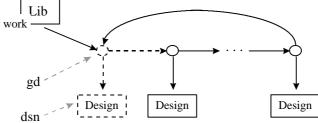

typedef Design\* did; typedef SLList<Design\*> gdid; int st = lib->add\_designs(dsn); int st = lib->sub\_designs(dsn); gdid gd = lib->gen\_designs();

Figure 12. Add, Subtract, and refer design units.

Figure 12 shows the C++ code for handling Design object and the result of that running. The type "did" is predefined to a pointer of Design object by PI library. And, the type "gdid" is also predefined to a pointer of a single linked list of Design objects. For the Lib object named "work", add routine adds the given Design object to the list within Lib object, sub routine subtracts the given Design object from the list, and gen routine returns the list of all Design objects contained in Lib object.

- Synopsis of add routine

- #include "libraryMan.h"

- #include "designMan.h"

- int lib->add\_designs(dsn)

- lid lib; -- pointer of a Lib object.

- did dsn; -- pointer of a Design object.

## Description

- a. Append a Design object to the list which is a storage field of a given Lib object.

- b. Return 1 if finished successfully, otherwise return 0.

- cf) If there is already a Design object which has the same name, it is an erroneous condition.

- Synopsis of sub routine

#include "libraryMan.h"

- #include "designMan.h"

- int lib->sub\_designs(dsn)

- lid lib; -- pointer of a Lib object.

- did dsn; -- pointer of a Design object.

## Description

- a. Subtract a Design object from the list of a given Lib object.

- b. Return 1 if finished successfully, otherwise return 0.

- Synopsis of gen routine

- #include "libraryMan.h"

- #include "designMan.h"

- gdid lib->gen\_designs()

- lid lib; -- pointer of a Lib object.

## Description

a. Collect the Design objects which is connected to a given Lib object as a list.

b. Return the pointers of Design objects as a single linked list.

## 5.1.3 Get Routine

The type of attribute fields is not a pointer type but integer, string, enumeration, and so on. The attribute value of a VDT object is determined when the object is created, and can be changed. So, there is only access routine to refer the attribute fields. The get routine is the access routine of the attribute fields.

- Synopsis of get routine

- #include "libraryMan.h"

```

string lib->get_name()

```

lid lib; -- pointer of a Lib object.

#### Description

a. Return the logical library name corresponding to a given Lib object.

cf) The above italic string "name" can be replaced to other strings in order to get the other attribute field.

## 5.1.4 Search Routine

As a design library is distinguished by a different logical name, a design unit is distinguished by a different design unit name. There are two methods to find a design unit contained in a design library. One is the sequential search of all Design objects, which can be obtained using gen routines. The other is by using the search routine which is defined as a member function of Lib object. Lib object internally has a symbol table for design units. The symbol table uses the name of design unit as a key. So, an easy and fast search can be accomplished only with the name of a design unit.

lid lib = gl.open("work"); did dsn = lib->search("alu", "behav");

Figure 13. Search a design unit.

Figure 13 shows the C++ code of search routine and the result. The Lib object "work" can first be obtained using open routine. To search for a design unit, two names are needed as parameters of search routine. The first name "alu" is a primary unit name, the second name "behav" is a secondary unit name. Namely, the searching design unit may be a architecture body named "behav" corresponding to an entity named "alu". If a primary unit wish to be obtained, the second name should not be given. In a design library, only one design unit can exist with the same name. So, the search routine returns just one Design object.

• Synopsis of search routine

#include "libraryMan.h"

#include "designMan.h"

did lib->search(str1[, str2])

lid lib; -- pointer of a Lib object.

char\* str1; -- identifier of primary unit.

char\* str2; -- identifier of secondary unit.

#### Description

a. Make a symbol corresponding to given design unit names.

b. Find a symbol by searching the symbol table contained in a given Lib object.

c. Return the pointer of the found Design object. Return Null pointer if not found.

cf) To search for a design unit in a given design library. The corresponding Lib object should first be opened. If not opened, it will return Null pointer because the Lib object does not yet have a list of Design objects.

## 5.1.5 Dump Routine

VDT data model defines the Lib object and its data structure. The storage fields of the data structure can be classified into attribute fields and relationship fields as other VDT objects. The dump routine prints the contents of the data structure of a given object. This routine may help in the development of VDT applications by providing an easy and fast debugging mechanism.

int st = lib->dump();

Design Library ...

name : work path : ./LIB designs : (ALU\_STATGE) (ALU\_STAGE\_BEHAVIOR) (ALU\_STAGE\_STRUCTURE) (TRAFFIC)(TLC) (TLC\_SPEC)

Figure 14. Text output of the contents of Lib object.

Figure 14 shows the C++ code of dump routine and the result for a Lib object. The attribute field "name" describes the logical library name "work". The attribute field "path" describes the directory path-name "./LIB" corresponding to the design library. The field "designs" represents the 1:m relationship to design units, and describes the list of Design objects linked to the Lib object. In the textual output, the symbols of Design objects are printed instead of Design objects itself. The symbol of a Design object is made by using the name of corresponding design unit. Namely, the symbol of a secondary unit is made by "the associated primary unit name" + "\_\_" + "the secondary unit name". The symbol of a primary unit is just its name. For instance, "TLC" may be an entity declaration. "TLC\_SPEC" may be an architecture body named "SPEC", whose associated entity declaration is called "TLC".

• Synopsis of dump routine

#include "libraryMan.h"

int lib->dump()

lid lib; -- pointer of a Lib object.

## Description

a. Print the contents of a given Lib object in textual form.

b. Return 1 if there is no error, otherwise return 0.

## 5.2 Design Unit Management

This module has few access routines and processing routines. As access routines, there are "load/save" routines, "create" routine, and "get" routine. As processing routines, there are "dump" routine and "check" routine.

A design unit is composed of a library unit and a context clause. A design unit certainly has an associated library unit. There are five kinds of VHDL construct called library unit. A library unit is either a primary unit or a secondary unit. VHDL constructs called primary unit include entity declaration, package declaration, and configuration declaration. Other constructs, architecture body and package body are called the secondary unit. A secondary unit is a separately analyzed body of a primary unit resulting from a previous analysis.

The design entity is the primary hardware abstraction in VHDL. It represents an individual hardware design that has well-defined inputs and outputs and performs a well-defined function.

A complete design is composed of one or more design entities, and is represented by a design hierarchy. A design entity may be described in terms of interconnected components. Each component of a design hierarchy may be bound to a lower level design entity. The bindings necessary to identify a design hierarchy can be specified in a configuration of the top level entity in the hierarchy.

A design hierarchy can be defined by a design entity or by configuration. A design entity is defined by an entity declaration together with a corresponding architecture body. There are associations between a primary unit and a corresponding secondary unit.

The name of a primary unit is given by the first identifier after the initial reserved word of that unit. As for the secondary units, only the architecture body is named. Each primary unit in a given design library must have a simple name that is unique within the given design library. Also, each secondary unit associated with a given primary unit must have a unique name, by which the name is assembled with the name of secondary unit and the name of associated primary unit.

|               | pname                    | sname                   | name          |

|---------------|--------------------------|-------------------------|---------------|

| entity        | entity<br>identifier     | architecture identifier | pname         |

| arch_body     | entity<br>identifier     | architecture identifier | pname + sname |

| package       | package<br>identifier    |                         | pname         |

| pack_body     | package<br>identifier    | package identifier      | pname + sname |

| configuration | configuration identifier | entity<br>identifier    | pname         |

Figure 15. Naming of a design unit.

Figure 15 shows the naming rule of a design unit. The data structure of Design object has many attribute fields such as, "object\_type", "pname", "sname", "name", and so on. These storage fields is for the identification of a design unit. The field "pname" stores the primary unit name. The field "sname" stores a secondary unit name. A design unit, which the associated library unit is a primary unit, has only "pname". If the associated library unit is a secondary unit, the design unit has "sname" and "pname", where the "pname" is the identifier of the associated primary unit.

The field "name" records a unique name for a design unit within a design library. The name is made by an assembly of primary unit name and secondary unit name. For instance, of a design unit associated with an architecture body, the name is an assembled string of "pname" and "sname" with separator "--", where "sname" is the identifier of the architecture body, and "pname" is the identifier of the associated entity declaration.

The design unit whose associated library unit is a primary unit does not have "sname". But the field "sname" is used for special purpose, a design unit associated with entity declaration uses the "sname" to record the identifier of an architecture body. This recording indicates the most recently analyzed architecture body associated to the entity declaration. This pair becomes a default design entity. Also, a design unit associated with configuration declaration uses the "sname" to record the identifier of associated entity declaration.

## 5.2.1 Load/Save Routine

Design object can be regarded as a container of Basic objects. A stored intermediate form is composed of one Design object and many Basic objects. The behavior of circuits are represented wholly by Basic objects and links among these objects which is called Basic cloud. The Basic cloud is a directed graph which contains only one Basic object corresponding to library units. This object is a top vertex of the graph, and Design object points to the top object using storage field "top".

Figure 16. Load and save a design unit.

Figure 16 shows the C++ code of load/save routines and the results. A created or opened Design object just contains no Basic objects, and the field "top" has Null pointer. If there is the intermediate form file corresponding to a design unit, the "load" routine reads the file, constructs an intermediate form, and records the field "top" to the pointer of a top object. The "save" routine stores a given Design object and the related Basic cloud to a intermediate form file. The contents of Design object are located at the header part of a file, and the contents of Basic cloud is appended to the file. The "open" routine for a design unit just reads the header part of the corresponding intermediate form file, and creates a Design object with that contents. In the future, the "load" routine will read the remainder of the file.

An intermediate form corresponding to a given design unit may have any external reference like that from O\_signal to O\_type, where the O\_type is not contained in the given design unit. The "save" routine breaks the external link during storing of a file, and the "load" routine restores the external links during reading.

- Synopsis of load routine

- #include "designMan.h"

- did dsn->load()

- did dsn; -- pointer of a Design object.

#### Description

a. Get a path-name of the intermediate form file from a given Design object.

- b. Check that the file is not corrupted by reading the contents of the header part.

- c. Reconstruct an intermediate form at the same time as when reading the remainder part of the file.

- d. Return the pointer of a given Design object if there is no error, otherwise return Null pointer.

- cf) During the reading of a given intermediate form file, there is any link to a Basic object which is contained in other Design object. The related design unit will be loaded automatically.

• Synopsis of save routine

#include "designMan.h"

did dsn->save()

did dsn; -- pointer of a Design object.

## Description

a. Get a path-name for the intermediate form file from a given Design object.

b. First save the contents of Design object in the header part of the file.

c. Save the contents of Basic cloud in the remainder part of the file.

d. Return the pointer of a given Design object if there is no error, otherwise return Null pointer.

#### 5.2.2 Create Routine

Design object is a container of Basic objects. The data structure of Design object has a storage field for Basic object list. The "create" routine creates a Basic object, and appends to the list of a given Design object. Each created Basic object is numbered sequentially, where the sequence number is unique within in a Design object. Actually, the Basic object list is implemented on to a linear table which is automatically and discretely extended.

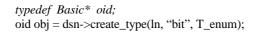

Figure 17. Create a Basic object.

Figure 17 shows the C++ code of "create" routine and the result. The type "oid" is predefined to a pointer of Basic object by PI library. The "create\_type" routine creates a Type object within a Design object pointed by variable "dsn". Type object has many attribute fields which must be filled during creation. As parameters in the above code, line number "5", type name "bit", and type kind "T\_enum" are given. Newly created Type object is appended to the last index of the linear table.

Synopsis of create routine

#include "designMan.h"

#include "basicMan.h"

oid dsn->create\_type(ln,str,tk)

did dsn; -- pointer of a Design object.

int ln; -- line number within VHDL file.

char\* str; -- identifier of type declaration.

type\_kind tk; -- kind of type declaration.

## Description

a. Create a Type object attributed by the given parameters.

b. Append the object to the Basic object list within a given Design object.

c. Return pointer of Type object if there is no error, otherwise return Null pointer.

cf) The above italic string "type" can be replaced into other strings to create other kinds of Basic object. All attribute fields of a created object must be given as parameters.

## 5.2.3 Get Routine

The type of attribute fields is not a pointer type but integer, string, enumeration, and so on. The attribute value of a VDT object is determined when the object is created, and can be changed. So, there is only access routine to refer the attribute fields. The get routine is the access routine of the attribute fields.

• Synopsis of get routine

#include "designMan.h"

string dsn->get\_pname()

did dsn; -- pointer of a Design object.

#### Description

a. Return the primary unit name corresponding to a given Design object.

cf) The above italic string "pname" can be replaced to other string for getting other attribute field.

## 5.2.4 Dump Routine

As other VDT objects, the data structure of Design object also has many attribute fields and a few relationship fields. The "dump" routine prints the contents of a given Design object in textual form. It will help to debug during the development of VDT applications.

```

int st = dsn->dump();

Design unit ...

type : entity

pname : ALU_STAGE

sname : STRUCTURE

path : ./LIB/ALU_STAGE.if

spath :

count : 171

top : 160

```

Figure 18. Textual output of the contents of a given Design object.

Figure 18 shows the C++ code of "dump" routine and the result. The attribute fields do not record the pointer value but integer or string value. The relationship fields record the pointers of related objects, where the related objects are only Basic objects. Instead of printing the pointer value of related object, the sequence number of that object is printed. This routine prints the contents of a Design unit pointed by variable "dsn", and return either success or fail.

```

• Synopsis of dump routine

```

#include "designMan.h"

```

int dsn->dump()

```

did dsn; -- pointer of a Design object.

## Description

a. Print the contents of a given Design object in textual form.

b. Return 1 if no occur, otherwise return 0.

## 5.2.5 Generate Routine

A design unit is composed of a context clause and a library unit. The "generate" routine for a Design object makes VHDL code corresponding to each Basic object contained in this object. If the given object does not have enough information, the generated VHDL code may contain illegal syntax and semantics.

• Synopsis of generate routine

#include "designMan.h"

void dsn->generate()

did dsn; -- pointer of Design object.

## Description

a. Generate the VHDL code from a given Design object "dsn".

b. Print the textual code to the screen by default.

## 5.2.6 Check Routine

The access routines located in primitive layer of PI library can be classified into two categories: attribute getting routines and relationship making routines. The relationship making routines check if the relationship for the given objects is legal to make. But only a few illegal syntax and semantics can be detected by relationship making routines.

All lexical and syntactic errors are detected by analyzer during parsing of VHDL code and constructing of an intermediate form. And, all semantic errors are detected by this "check" routine. The "check" routine is located in application layer of PI library, and does the semantic checking for each Basic object contained within the given Design object.

• Synopsis of check routine

int dsn->check()

did dsn; -- pointer of a Design object.

## Description

a. Get Basic objects contained within the given Design object.

b. Check semantics for each Basic object.

c. Print error message for each semantic error.

d. Return 1 if there is no error, otherwise return 0.

## 5.3 Library Unit Management

This module has numerous access routines and processing routines. As access routines, there are "set/get" routine, "add/sub/gen" routine, and "get" routine. As processing routines, there are "search", "dump", "generate", and "check" routine.

All VHDL constructs, except for design unit and design library, are represented by Basic objects in an intermediate form. Basic object is classified into many kinds, and identified by the value of storage field "object type". And some kind of objects are more classified by many kinds: "operator kind", "literal kind", and so on.

A declarative region is a portion of the text of the VHDL description. A declarative region is formed by the text of each of the several VHDL constructs, such as entity declaration, process statement, block configuration, and so on. The declarative region is said to be associated with the corresponding declaration or statement.

A declarative region is represented by the symbol table, which is located within a Basic object associated with the declaration region. The symbol table of a Basic object enrolls All VHDL constructs having names and appearing within the corresponding VHDL construct. There is hierarchy among declarative regions. For instance, a declarative region associated with entity declaration is larger than the region associated with process statement. Likewise, there is hierarchy among Basic objects having symbol table.

The scope of a declaration is a portion of the text in which the declaration may be visible. A named entity can be visible only within its own scope. A declaration appears with a declaration region associated with a certain VHDL construct. Namely, the scope of a named entity may be the declarative region appearing the declaration. The Basic object corresponding to a named entity is enrolled in to the symbol table, in which the declaration of the named entity appears within the declarative region corresponding to the symbol table.

#### 5.3.1 Set/Get Routine

The storage fields for representing 1:1 relationship can record only one pointer of Basic object. The records of these fields can be modified by "set" routine, and can be referred by "get" routine.

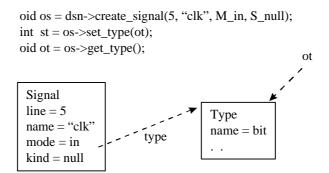

Figure 19. Set and refer a Basic object.

Figure 19 shows the C++ code of "set/get" routine and the results. The "create\_signal" routine creates a Signal object named "clk", and returns the pointer "os" of the created object. For the object "os", the "set\_type" routine makes a 1:1 relationship with a given Type object "ot". The "get\_type" routine returns the Type object related to "os" object.

• Synopsis of set routine

#include "basicMan.h"

- int obj->set\_*type*(obt)

- oid obj; -- pointer of Basic object.

- oid obt; -- pointer of Basic object.

# Description

a. Link the given object "obt" to the storage field "type" of "obj" object.

b. Print error message if "obj" object does not have the "type" relationship.

c. Print error message if the given "obt" object is illegal as Type object.

c. Return 1 if there is no error, otherwise return 0.

cf) The above italic string "type" can be replaced into other relationship names to make a 1:1 relationship.

• Synopsis of get routine

#include "basicMan.h"

```

oid obj->get_type()

```

oid obj; -- pointer of Basic object.

#### Description

a. Get the object linked to the storage field "type" of a given object "obj".

b. Report error if the object "obj" does not have a relationship named "type".

c. Return the linked object if there is no error, otherwise return Null pointer.

cf) The above italic string "type" can be replaced into other relationship names to get the 1:1 relationship field.

### 5.3.2 Add/Sub/Gen Routine

The storage fields for representing 1:m relationship can link one more Basic object. The records of these fields can be modified by "add/sub" routine, and can be referred by "gen" routine.

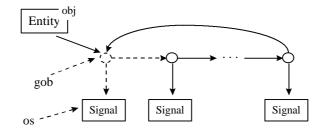

int st = obj->add\_signals(os); int st = obj->sub\_signals(os); gid gob = obj->gen\_signals();

Figure 20. Append, detach, and refer Basic objects.

Figure 20 shows the C++ code of "add/sub/gen" routine and the results. The "add\_signals" routine appends the given Signal object "os" to the list of Entity object "obj". The "sub\_signals" routine detaches the given Signal object "os" from this list. The "gen\_signals" routine returns the copy "gob" of this list.

- Synopsis of add routine

- #include "basicMan.h"

- int obj->add\_*signals*(obs)

- oid obj; -- pointer of Basic object.

- oid obs; -- pointer of Basic object.

### Description

- a. Append the given object "obs" to the signal list of object "obj".

- b. Report error if the object "obj" does not have a 1:m relationship for signal list.

- c. Report error if the given object "obs" cannot be regarded as Signal object.

- d. Return 1 if there is no error, otherwise return 0;

cf) The above italic string "signals" can be replaced into other relationship names to make the 1:m relationship.

- Synopsis of sub routine

- #include "basicMan.h"

- int obj->sub\_types(obt)

- oid obj; -- pointer of Basic object.

- oid obt; -- pointer of Basic object.

### Description

a. Detach the given object "obt" from the type list of object "obj".

b. Report error if the object "obj" does not have a 1:m relationship for type list.

c. Return 1 if there is no error, otherwise return 0.

cf) The above italic string "types" can be replaced into other relationship names to remove the 1:m relationship.

• Synopsis of gen routine

#include "basicMan.h"

gid obj->gen\_signals()

oid obj; -- pointer of Basic object.

### Description

a. Copy this signal list of object "obj".

b. Report error if the object "obj" does not have a 1:m relationship for signal list.

c. Return the signal list if there is no error, otherwise return empty list.

cf) The above italic string "signals" can be replaced into other relationship names to refer the 1:m relationship.

# 5.3.3 Get routine

The storage fields for representing attribute can record one value which should be of a certain type. The records of these fields can be accomplished during the creation time of Basic object. Afterward, these records cannot be modified and can only be referred by "get" routine.

• Synopsis of get routine

#include "basicMan.h"

char\* obj->get\_name()

oid obj; -- pointer of Basic object.

## Description

a. Get the string value of attribute field "name".

b. Report error if the object "obj" does not have a attribute field named "name".

c. Return the value if there is no error, otherwise return Null string.

cf) The above italic string "name" can be replaced into other attribute names to get the attribute field. The type of returned value is related to the attribute field.

### 5.3.4 Search Routine

The "search" routine can easily find a named object by searching the symbol table of a given object. This routine may search globally with option "Global" by traversing the hierarchy and searching each symbol table.

typedef SLList<oid\*> gid; oid obj = dsn->get\_top(); gid gob = obj->search("bit", Global);

Figure 21. Search a named object.

Figure 21 shows the C++ code of "search" routine and the result. The "search" routine searches globally an object named "bit" with option "Global" by traversing the scope hierarchy. The traversing may be over to other design unit. This routine collects all objects named "bit" and return the object list in order, in which the object appearing in lowest region of scope hierarchy is first in the list.

• Synopsis of search routine

#include "basicMan.h"

gid obj->search(str, opt)

char\* str; -- name of Basic object.

int opt; -- option of searching.

# Description

a. Search a given named object contained within a Basic object "obj".

b. Traverse to the upper region of object "obj" if with global option.

c. Make the list of found objects by searched order.

d. Return the list if there is no error, otherwise return empty list.

cf) This routine is defined only for the objects corresponding to VHDL constructs that have a declarative part. In other words, this routine can be invoked for a given object that is included in Region group.

## 5.3.5 Dump Routine

The data structure of each Basic object has many attribute fields and many relationship fields. The "dump" routine prints the contents of a given Basic object in textual form. It will help in the development of VDT applications.

```

int st = obj->dump();

Attribute

object_type : entity

id_number : 160

line_number : 1

flag

:0

: ALU_STAGE

name

symbols

: (163,S1) (162,S2) (166,B1) (161,S3)

(168,M)(167,C1) (164,S0) (165,A1) (169,C2) (170,F1)

Relationship

scope

: 0

context

generics

:

ports

: 161 162 163 164 165 166 167 168 169 170

subprograms :

types

constants

:

signals

files

aliases

attributes

attr_specs

disc_specs

uses

```

Figure 22. Textual output of the contents of Entity object.

Figure 22 shows the C++ code of "dump" routine and the result. The "dump" routine prints the contents of a given Basic object, Entity object in this figure. Entity object has a symbol table because the corresponding entity declaration is associated with a declaration region.

• Synopsis of dump routine

#include "basicMan.h" void obj->dump()

oid obj; -- pointer of Basic object.

## Description

a. Print the contents of a given Basic object in textual form.

b. Return 1 if there is no error, otherwise return 0.

## 5.3.6 Generate Routine

All kinds of Basic objects each have a corresponding VHDL construct. The "generate" routine for a Basic object makes the corresponding VHDL code from the information contained in the object. If the given object does not have enough information, the generated VHDL code may contain illegal syntax and semantics.

Synopsis of generate routine #include "basicMan.h" void obj->generate() oid obj; -- pointer of Basic object.

#### Description

a. Generate the VHDL code from a given Basic object "obj".

b. Print the textual code on the screen by default.

### 5.3.7 Check Routine

All kinds of Basic objects each have a corresponding VHDL construct. The "check" routine for a Basic object checks the all semantics of corresponding VHDL construct.

• Synopsis of check routine

#include "basicMan.h"

void obj->check()

oid obj; -- pointer of a Basic object.

#### Description

a. Check the semantics for a given Basic object "obj".

b. Print proper message immediately when error is detected.

c. Return no value.

## 5.3.8 Characterize Routine

Basic objects are classified into many kinds according to various properties of VHDL constructs. For instance, a named entity -- such as, signal, type, variable, and so on. -- can be referred by other portion of VHDL construct. These Basic objects can be grouped and called named object. Another example, a typed entity -- such as signal, variable, subprogram, and so on. -- has a relationship to Type object. These objects can be grouped and called typed object. The typed object can only appear in an expression.

There are numerous routines that get the properties from a given Basic object. The VDT user may get the properties by digging all the attribute fields and relationship fields for a given object. But it is easy to use these routines to get various properties.

- Synopsis of characterize routine

- #include "basicMan.h"

int obj->hasScope()

int obj->isSequStmt()

#include "glossary.h"

int isStaticExpr(obj)

oid getExprType(obj)

oid obj; -- pointer of Basic object.

## Description

- a. The "has" routine returns if a given Basic object has "scope" field.

- b. The "is" routine returns if a given object belongs to sequential statement group.

- c. The third "is" routine returns if a given object belongs to static expression group.

- d. The "get" routine returns the Type object related to a given expression.

- cf) The above italic strings can be replaced into other strings to get other properties.

# 6 Characterize Routines

Lib object and Design object cannot be divided any further. But Basic object is classified into many kinds. Each object corresponds to a unique VHDL construct, and also has the properties which the corresponding construct has. For instance, an object has a name, an enclosing region, a specified type, and so on. In a detail, an object belongs to the group of expression, sequential statement, scalar type, and so on. Basic object can be classified not only by object kinds, but also by these properties.

All kinds of Basic objects are implemented to classes derived from a same base class named "Basic". These objects are viewed to user just as the same object. In many cases, the user wants to know the kind of a given Basic object and the properties of that object. The user can find these information by digging the storage fields of a given object. But it is easy to use the "characterize" routines that find any properties from a given object. These "characterize" routines are classified into three kinds: class identifying routines, group identifying routines, and property getting routines.

Class identifying routines identify that a given object belongs to a specified class. There are many intermediate classes defined just for code sharing. These routines are accomplished just by checking the class hierarchy. Group identifying routines identify that a given object belongs to a specified group. Basic objects having the same properties are grouped together, and are said to belong to any group. This can be accomplished by digging only attribute fields of a given object. Property getting routines get any specified properties from a given object by digging into the relationship fields of that object.

All attribute fields of VDT object are determined at the time of creation, and cannot be changed afterwards. So first and second routines always guarantee a correct result and errorless completion. These routines are used for the relationship checking that is accomplished within relationship making routines.

On the other hand, the relationship fields are changed freely by using the relationship making routines. This meas that property getting routines cannot guarantee correct results. For instance, if a given object does not have enough information represented by relationships, then these routines cannot obtain any properties.

## 6.1 Class identifying routines

The inheritance mechanism of object-oriented technique enables the code sharing. The common storage fields and member functions can be defined as an individual class. All classes derived from a class inherit all storage fields and member functions of that class.

In addition, the inheritance mechanism enables the grouping of objects that have some common properties. All objects corresponding to classes derived from a class are said to belong to that class.

For a given object, it usually needs to know if the corresponding class inherit a specified class, in other words, belongs to a specified class. Through the following "has" routine, a given object has some specified storage fields and member functions, in other words, belongs to a specified class.

- Synopsis of "has" routines.

- int obj->hasClassName();

- oid obj; -- pointer of a Basic object.

### Description

a. These routines return 1 if a given object belongs to the specified class, otherwise return 0.

cf) The italic string can be replaced into other class names to identify other classes.

Figure 23. Class hierarchy of Basic objects.

Figure 23 shows the class hierarchy of Basic object. All classes are derived from the same class named "Basic". All terminal classes corresponds to some kind of Basic objects. The intermediate classes are defined for code sharing. Namely, these classes have common storage fields and member functions that are shared by multiple classes. The following list are all intermediate classes defined by the above class hierarchy.

## Context

This class contains a relationship field named "context" and several member functions. This field makes the

relationship to an object that corresponds to context clause. All classes corresponding to library units inherit this class.

### • Symbols

This class contains a relationship field named "symbols" and several member functions. This field makes a relationship to object list that corresponds to named entities. All classes corresponding to VHDL constructs that contain a declarative part inherit this class.

#### Uses

This class contains a relationship field named "uses" and several member functions. This field makes a relationship to object list that corresponds to use clauses. All classes corresponding to VHDL constructs that may contain one or more use clauses inherit this class.

#### Comments

This class contains a relationship field named "comments" and several member functions. This field makes a relationship to object list that corresponds to comments. All classes corresponding to VHDL constructs that may contain one or more comments inherits this class.

### Scope

This class contains a relationship field named "scope" and several member functions. This field makes a relationship to an object that corresponds to enclosing region. All classes corresponding to VHDL constructs that have an enclosing region inherit this class.

#### Name

This class contains a attribute field named "name" and member functions. This field records the name of an object. All classes corresponding to VHDL constructs that may have a name inherit this class.

### Type

This class contains a relationship field named "type" and several member functions. This field makes a relationship to an object that corresponds to a type declaration. All classes corresponding to VHDL constructs that have a specified type inherit this class.

## 6.2 Group identifying routines

Basic objects having the same properties are grouped together, and are said to belong to the same group. For instance, the constraint in VHDL takes a role of constraining the range of the specified type. The constraints are described by several objects according to the text of constraint. These objects are grouped and are said to belong to a Constraint group.

As another example, an expression in VHDL is composed of operators and operands. Each operator and operand has a value and a type. The objects corresponding to operators or operands are grouped and are called Expression object. As the objects corresponding to operands of an operator, the objects included in Expression group are only allowed.

It usually needs to know if a given object belongs to any specified group. The following "is" routine provides this function.

- Synopsis of "is" routines

- int obj->isGroupName();

oid obj; -- pointer of Basic object.

## Description

a. These routines return 1 if a given object belongs to the specified group, otherwise return 0.

cf) The italic string can be replaced into other group names to identify other groups.

In special, the following routines are defined to identify that a given object is the object having specified kind. These routines are defined as virtual functions with a different argument.

virtual int isRight(const object\_type) const; virtual int isRight(const literal\_kind) const; virtual int isRight(const operator\_kind) const; virtual int isRight(const stmt\_kind) const; virtual int isRight(const subprog\_kind) const; virtual int isRight(const type\_kind) const;

Figure 24 shows the groups that are classified Basic objects according to attribute fields only. All defined groups are listed as follows.

Figure 24. Classifying Basic objects by multiple groups.

## Choice

This group includes the objects corresponding to choice in VHDL. A choice constraint can be a simple expression or a discrete range.

#### Constraint

This group includes the objects corresponding to constraint in VHDL. A constraint can be a range constraint or an index constraint.

#### • RangeConstraint

This group includes the objects corresponding to range constraint in VHDL. An index constraint can be a To/Downto range or an range attribute. The range attributes imply attribute names that result in a range.

## IndexConstraint

This group includes the objects corresponding to index constraint in VHDL. An index constraint is represented by OP\_range which describes a discrete range.

### • Expression

This group includes the objects corresponding to an expression in VHDL. An expression is composed of operators, operands, and names. The names denote objects, values, and attributes. The only attribute names allowed as expression are ones that result in a value.

## • Type

This group includes the objects corresponding to a type in VHDL. All objects included in an expression group have a value and a type. The types imply the declarations, or attribute names that result in a type.

## • Region

This group includes the objects corresponding to VHDL constructs that have a declarative part. Only these objects have the "search" member function.

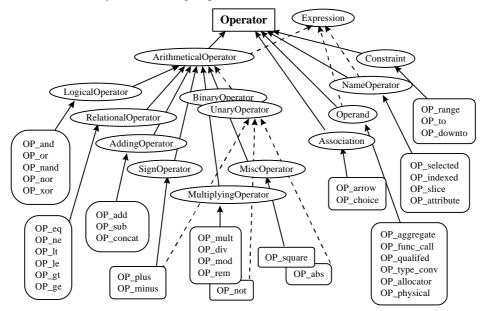

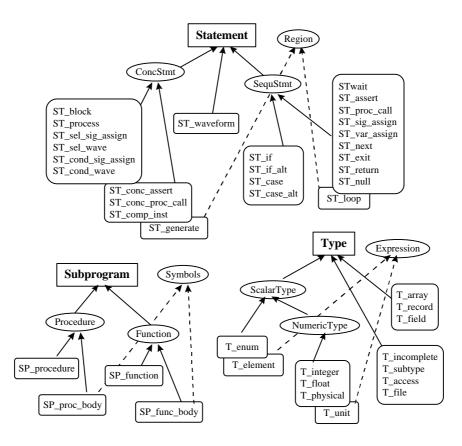

Figure 25, 26 show the groups that are classified as Operator, Statement, Subprogram, and Type objects according to attribute fields only. All defined groups are listed as follows.

Figure 25. Classifying Operator objects by multiple groups.

Figure 26. Classifying Statement, Subprogram, and Type objects by multiple groups.

## ArithmeticalOperator

This group includes the objects corresponding to operators in VHDL. The operators are classified according to the precedence level of seven groups: LogicalOperator, RelationalOperator, ShiftOperator, AddingOperator, SignOperator, MultiplyingOperator, MiscellaneousOperator. According to existence of left operand, the operator are classified by two groups: UnaryOperator, BinaryOperator.

#### Operand

This group includes the objects corresponding to operands in VHDL. The operand is classified into aggregates, function calls, qualified expression, type conversion, allocators, and physical literal.

### NameOperator

This group includes the object corresponding to name in VHDL. The name is classified into selected name, indexed name, slice name, and attribute name.

### Association

This group includes the objects corresponding to association constructs in VHDL. A OP\_arrow describes an association of a generic, a port, or a parameter. A OP\_choice describes an element association that appears in an

aggregate construct.

## • SequStmt

This group includes the object corresponding to sequential statements. Sequential statements are used to define algorithms for the execution of a subprogram or process. They execute in the order in which they appear.

ConcStmt

This group includes the objects corresponding to concurrent statements. Concurrent statements are used to define interconnected blocks and processes that jointly describe the overall behavior or structure of a design. They execute asynchronously with respect to each other.

## • Function

This group includes the objects corresponding to function. These objects are SP\_function, ST\_func\_body.

## • Procedure

This group includes the objects corresponding to procedure. These objects are SP\_procedure, SP\_proc\_body.

## • ScalarType

This group includes the objects corresponding to scalar types in VHDL. Scalar types consist of enumeration types, integer types, physical types, and floating point types.

• NumericType

This group includes the objects corresponding to numeric types in VHDL. Numeric types consist of integer types, floating point types, and physical types.

# 6.3 **Property getting routines**